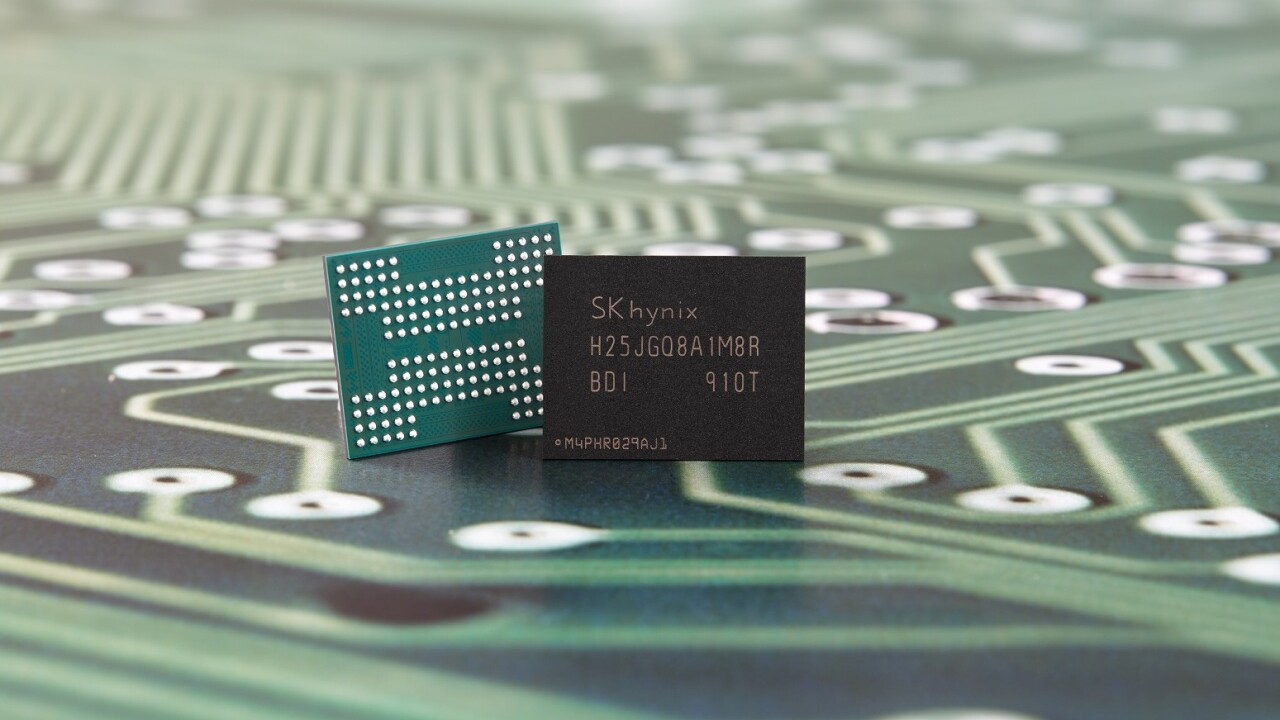

SK Hynix: 96-Layer-QLC-Speicher alias „4D NAND“ wird bemustert

Der südkoreanische Speicherhersteller SK Hynix liefert seinen ersten QLC-NAND-Flash zur Bemusterung an SSD- und Controller-Hersteller aus. Der 3D-NAND speichert 4 Bit pro Speicherzelle, die wiederum in 96 Ebenen (Layer) angeordnet sind. Pro Chip wird eine Speicherkapazität von 1 Terabit geboten.

3D-QLC-NAND mit 96 Layern nennt SK Hynix „4D-NAND“

Die 96-Layer-Generation nennt SK Hynix selbst „4D-NAND“, was jedoch irreführend ist, denn technisch ist der Speicher mit 3D-NAND anderer Hersteller vergleichbar. Im vergangenen Jahr hat SK Hynix mit der Serienfertigung von 96-Layer-Chips begonnen, die aber zunächst als TLC-Variante mit 3 Bit pro Zelle und 512 Gigabit pro Chip erschienen. Wann die neue QLC-Variante in die Massenproduktion geht, lässt die Ankündigung offen. Eine eigene SSD auf Basis des QLC-Flash sowie mit eigenem Controller samt Firmware will SK Hynix erst im kommenden Jahr auf den Markt bringen. Sie soll dann den Sektor der Enterprise-SSDs mit mindestens 16 TB Speicherplatz bedienen und den HDDs Konkurrenz machen.

We plan to launch our own QLC-based SSD from next year when demand for enterprise QLC NAND is expected to become meaningful, [...] In particular, we intend to establish a solid position in the market for high-density eSSD, which is replacing hard disk drives (HDD), with NAND Flash solutions as large as 16TB (terabytes) or larger.

Han Joo Na, Head of NAND Development Strategy Office bei SK Hynix

SK Hynix macht keine näheren Angaben zur Chipgröße, spricht aber davon, dass der eigene QLC-NAND eine Chipfläche besitzt, die weniger als 90 Prozent der Fläche anderer QLC-Produkte entspricht. Bei der Speicherdichte, wesentlicher Maßstab für die Herstellungskosten pro Bit, spielt aber nicht nur die Chipgröße, sondern auch die Speicherkapazität des Chips eine Rolle. Western Digital und Toshiba dürften dank 1,33 Terabit trotz größerer Chips bei der Speicherdichte von 3D-NAND weiter führen. Auch Intel und Micron sowie Samsung haben QLC-NAND im Programm.

4-Plane-Architektur gegen Schreibschwäche von QLC

Der Wechsel von 3 Bit (TLC) auf 4 Bit (QLC) pro Speicherzelle macht den Speichervorgang komplexer, was Nachteile bei Schreibleistung und Lebensdauer (den möglichen Schreibzyklen) bedeutet. Während aufwendige Maßnahmen zur Fehlerkorrektur wie LDPC-Engines im SSD-Controller die Haltbarkeit in einem für viele Einsatzgebiete erträglichen Rahmen halten, setzten die NAND-Hersteller beim Design der Chips auf Kniffe zur Steigerung der internen Übertragungsraten. Dazu zählt der neu aufgelegte Trend, den Speicherbereich auf dem Die in noch mehr sogenannte Planes aufzuteilen, um mehr parallele Zugriffe und somit eine höhere Leistung zu ermöglichen. Toshiba will vom derzeit üblichen 2-Plane-Design ab der nächsten Generation (BiCS5) auf ein 4-Plane-Design wechseln.

SK Hynix nutzt bereits beim jetzt angekündigten 96-Layer-QLC-NAND wie auch den vorherigen Generationen ein 4-Plane-Design. Damit sollen die Speicherchips nicht nur bei den Kosten, sondern auch bei der Leistung konkurrenzfähig sein. Auch bei Micron/Intel und Samsung kamen schon 4 Planes zum Einsatz. Um einen Pseudo-SLC-Cache, bei dem ein Teil des Flash-Speichers mit nur einem Bit pro Zelle beschrieben wird, werden SSDs mit dem neuen QLC-Flash aber wohl trotzdem nicht herumkommen. Diese Form des Schreibpuffers hat sich schon bei TLC durchgesetzt.

Using small-sized planes, an advantage of the Company's 4D NAND, SK Hynix also adopted a four-Plane architecture. It increases the number of planes in a single chip from two to four, doubling data bandwidth from 32KB (kilobytes) to 64KB. With this high-performance product that can process up to 64KB of data simultaneously, SK Hynix secured both cost and performance competitiveness.

| Hersteller | Generation | Layer | Bit/Zelle | Kapazität/Die | Die-Fläche | Dichte |

|---|---|---|---|---|---|---|

| Toshiba/WD | BiCS3 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 768 Gbit |

132 mm² ? |

3,9 Gbit/mm² ? |

| BiCS4 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit 1,33 Tbit |

86,1 mm² 158,4 mm² |

5,9 Gbit/mm² 8,5 Gbit/mm² |

|

| BiCS5 | 128 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

66 mm ² ? |

7,8 Gbit/mm² ? |

|

| Samsung | V-NAND V4 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 1 Tbit |

128,5 mm² 181,9 mm² |

4,0 Gbit/mm² 5,6 Gbit/mm² |

| V-NAND V5 | 96 | 3 (TLC) 4 (QLC) |

256 Gbit bis 1 Tbit |

? | ? | |

| V-NAND V6 | 110+ | 3 (TLC) | 512 Gbit | 101,58 mm² | 5,0 Gbit/mm² | |

| Intel/Micron | Gen 2 | 64 | 3 (TLC) 4 (QLC) |

256/512 Gbit 1 Tbit |

59 mm² (256 Gbit) ? |

4,3 Gbit/mm² (256 Gbit) ? |

| Gen 3 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

? | ? | |

| SK Hynix | 3D V4 | 72 | 3 (TLC) | 256/512 Gbit | ? | ? |

| 3D V5 („4D“) | 96 | 3 (TLC) 4 (QLC) |

512 Gbit/1 Tbit 1 Tbit |

? | ? | |

| YMTC | Gen 1 | 32 | ? | ? | ? | ? |

| Gen 2 | 64 | 3 (TLC) | 256 Gbit | ? | ? |